新浪数码讯 7月5日晚间消息,台积电(TSMC)2022年技术论坛近期开幕,因为疫情缘故,本次依然是一场线上大会。

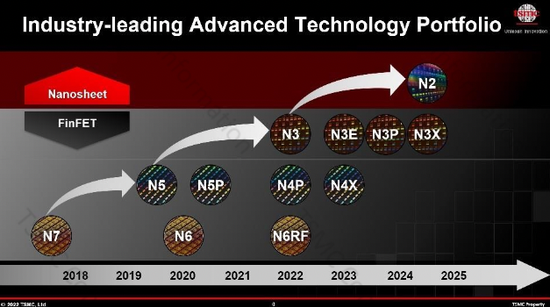

本年度的技术论坛上,台积电宣告了7nm至2nm工艺现状和规划等。其中最受关注的2nm工艺将在2025年量产。

台积电提到,在过去的两年里,新冠疫情加速了数字化转型,影响渗透至各个产业。虽然疫情对人类不是好事,但因为疫情存在。在这段时间里,科技的进步大幅地帮助和改变了企业及人们的工作方式,不再受到距离的限制。

另外,全球半导体产业的营收大幅增加,根据Gartner的数据,产业营收增长率超过25%。并且他们认为此趋势还将在这十年的剩余时间内持续下去,2030 年以前预计达到年营收1兆美元。

并且随着装置变得更智能、更高度连接,对于更具智能性的边缘装置和大规模运算能力需求越来越高。因此,高能效能耗变得更为重要。

结构性增长导致了先进和成熟工艺制程供不应求。因此,成熟工艺制程的成本结构现在反映了尖端技术的情况,在这种情况下,产能扩张意味着必须扩建新的晶圆厂。为了满足不断变化的市场需求,台积公司不断增加研发投资,并持续扩大对先进工艺制程和成熟工艺制程产能的投资。

台积电在本次大会上回顾了之前技术喝不同的制程工艺,如7纳米的相关产品组合不断扩大,从智能手机、CPU、GPU 和 XPU,延伸至射频和消费电子应用。2022 年底以前,产品设计定案的累积数量将超过 400。

5纳米技术已经进入量产的第三年,智能手机、5G、AI、网络和高性能计算产业的产品应用。

台积电将大量生产的经验不仅应用于良率的提高,持续提升N5和N4技术,预计到今年年底将有超过150个产品设计定案。

另外,衍生出的N4、N4P和N4X等技术加入5纳米家族,从N5到N4X,性能提升15%,芯片密度提高了6%,同时保持设计规则的兼容 性,以实现设计再利用、更多功能和更佳的规格提升。

台积电还面向汽车产业应用升级推出了最先进的N5A汽车平台计划,相关设计生态系统预计在今年第三季度通过AEC-Q100 Grade-2等级认证。

3纳米家族工艺技术持续采用FinFET半导体结构。台积电宣称N3工艺按计划顺利推进,将于2022 年下半年量产。N3E于2023年下半年量产。

今年台积电在3纳米技术上推出了TSMC FINFLEXTM架构这一创新,它结合工艺制程和设计的创新,提供了极致的设计弹性,从而优化高性能、低功耗或达到两者的平衡。

TSMC FINFLEX架构将3纳米家族技术的产品性能、功率效率和密度进一步提 升,让芯片设计人员能够在相同的芯片上利用相同的设计工具来选择最佳的鳍 结构支持每一个关键功能区块,分别有 3-2 鳍、2-2 鳍、以及 2-1 鳍结构可供选择。

另外,最受关注的2纳米制程,台积电也公布了相关信息。他们提到在过去的15年中,一直在研究纳米片(nanosheet)晶体管,“并建立了坚实的能力“。

N2的开发按计划顺利推进,预计于2025年量产。 相较于N3E,在相同功耗下速度提升10-15%,或在相同速度下功耗降低25-30%。

为了积极解决关键工艺制程的间距缩小问题,台积电在N7+开始利用EUV曝光设备和多重曝刻技术。台积公司将在2024年引进High-NA EUV曝光设备,以开发客户所需的相关基础架构和曝刻解决方案,以支持创新。