原标题:新思科技3DIC Compiler通过三星多裸晶芯片集成流程认证

【TechWeb】12月10日消息,新思科技(Synopsys)近日宣布,其集成了2.5D和3D多裸晶芯片封装协同设计和分析技术3DIC Compiler平台已通过三星多裸晶芯片集成(MDI™)流程认证,以助力面向高性能计算、AI和5G等计算密集型应用SoC的创新。基于此,双方共同客户能够通过统一的3DIC设计平台高效管理复杂的2.5D和3D设计,支持数千亿晶体管设计,并达成更佳PPA目标和扩展性能。

多裸晶芯片集成是指将多个裸晶芯片堆叠并集成在单个封装中,以满足在PPA、功能性、外形尺寸和成本方面的系统要求。在这种模式下,终端产品可模块化灵活组合,将不同的技术混合和匹配成解决方案,以满足不同的市场细分或需求。3DIC Compiler是一套完整的端到端解决方案,可实现高效的多裸晶芯片设计和全系统集成。它建立在高度集成的新思科技Fusion Design Platform™的通用、可扩展的数据模型之上,支持多裸晶芯片的协同设计和分析,为3D可视化、设计早期探索、规划、具体实现、设计分析和签核提供统一无缝集成的环境。

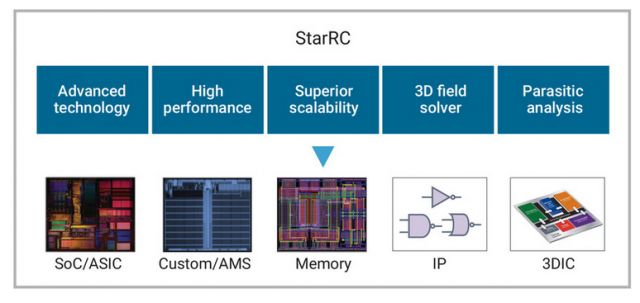

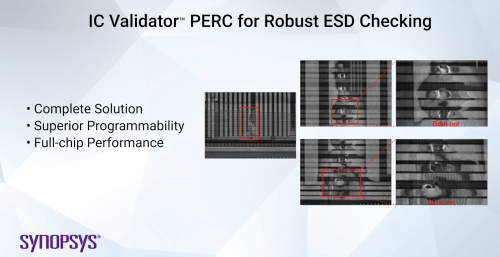

3DIC Compiler平台集成了StarRC™和PrimeTime®黄金签核解决方案,氪为多裸晶芯片提取寄生参数及静态时序分析(STA);采用Ansys® RedHawk™-SC和HFSS技术进行电迁移/电压降(EMIR)分析、信号完整性/电源完整性(SI/PI) 分析及热分析;内置PrimeSim™ Continuum用以电路仿真,并集成了IC Validator™用以设计规则检查(DRC) 、电路布局验证(LVS) ;同时还包含了新思科技TestMAX™支持IEEE1838多裸晶芯片测试设计标准的DFT 解决方案。

3DIC Compiler作为新思科技Fusion Design Platform的一部分,与Fusion Compiler™结合使用可扩展实现多裸晶芯片RTL-to-GDSII的协同优化。此外,该解决方案还提供DesignWare®Foundation、112G USR/XSR Die-to-Die和HBM2/2E/3IP、SiliconMAX™ In-Chip Monitoring and Sensing IP,并支持集成光电技术。更广泛的解决方案可通过新思科技Verification Continuum®平台提供硬件和软件协同验证、功率分析和系统物理原型设计。3DIC Compiler平台和更广泛的芯片实现产品组合都是新思科技Silicon to Software™战略的一部分,旨在助力开发面向未来的半导体和软件产品。