封面来源|Pexels

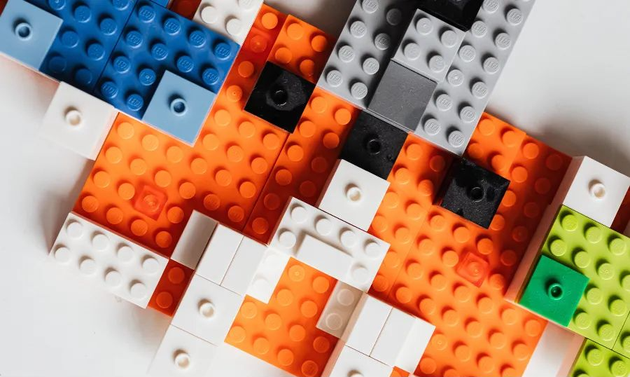

封面来源|Pexels当造芯变成拼乐高。

文|郑灿城编辑|彭孝秋

来源:36氪

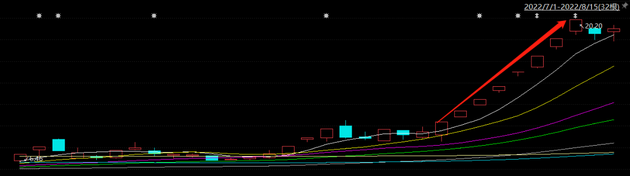

股价从9元涨到20元,仅用一周多时间。这就是Chiplet概念的魅力。

(大港股份8连涨停,数据来源:东方财富)

(大港股份8连涨停,数据来源:东方财富)但该公司(大港股份,002077.SZ)却在回函深交所时表示,自己未涉及Chiplet相关业务。

(大港股份回函节选,资料来源:东方财富)

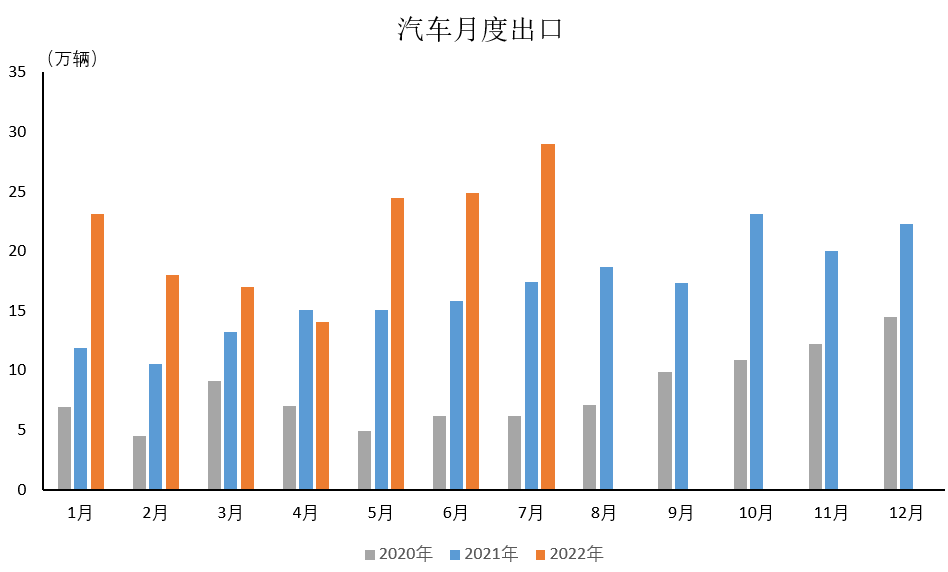

(大港股份回函节选,资料来源:东方财富)作为新的市场主线,Chiplet也为半导体指数大涨贡献了新动力。整个指数从8月1日至8月8日,涨幅超过17%。IP授权也是受益Chiplet的细分板块,头部企业芯原股份(688521.SH)也随之从44元涨到72元,涨幅达63%。

(半导体指数(801081.SWI)走势图,数据来源:东方财富)

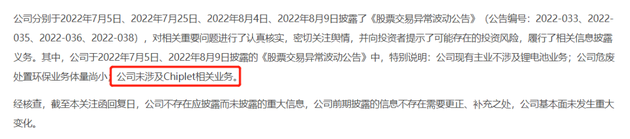

(半导体指数(801081.SWI)走势图,数据来源:东方财富)何为Chiplet?这个概念最早由美满电子Marvell(MRVL.O)创始人于2015年提出,但却在近期签署的《2022年芯片与科学法案》被提及。即美国总统科学技术顾问委员会(PCAST)开始“倡议建立Chiplet平台”。

(法案内容节选,图源网络)

(法案内容节选,图源网络)后摩尔时代的钥匙

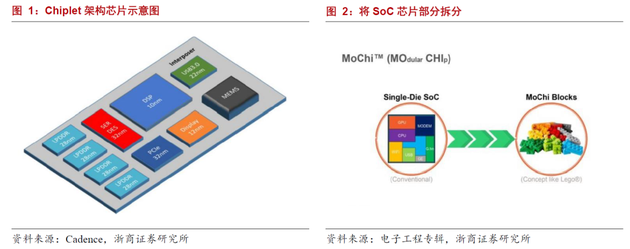

Chiplet翻译过来就是“芯粒”,其核心思路为乐高的模块化——将数个小芯片通过封装技术拼装成大芯片,以实现性能的提升和成本的降低。

在认识Chiplet之前,我们先要熟悉半导体行业的几个概念。一个是集成电路发展一直遵循的一条路线——摩尔定律。“每经过18-24个月,芯片内晶体管的数量就会增加一倍”。这个定律提出者为英特尔创始人戈登·摩尔(Gorden Moore),1965年时他还在仙童半导体公司任职。

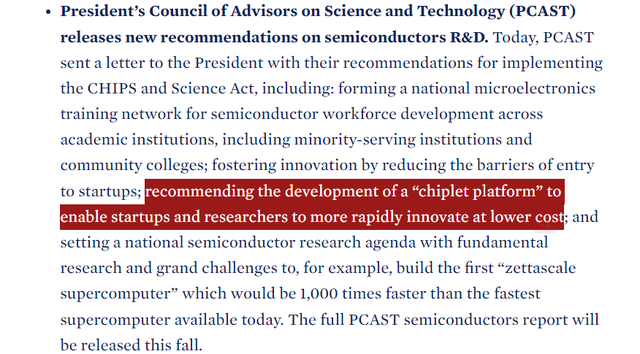

另一个是晶体管,作为芯片主要组成部分,晶体管的数量直接影响芯片性能。因此,自芯片被发明以来,科学家们就想尽办法在一定面积里塞下更多的晶体管。简单来说,如下图绿色部分,宽度越小,单位面积内能塞下的晶体管数量就越多,芯片的性能也就越高。

(示意图,图源网络)

(示意图,图源网络)这个宽度又叫制程,或是技术节点。经过晶圆厂对技术节点的不断突破,时至今日,虽然头部芯片制造厂商台积电和三星的战场已经来到了3nm,但相邻技术节点突破的时间间隔越来越长,即摩尔定律放缓。

(晶体管数量走势图,资料来源:Wikipedia、民生证券研究院)

除此之外,这个突破过程中,每一个制程的研发到量产都需要花费巨额的资本投入,节点的突破也就和资本的投入不成正比。36氪了解到,5nm制程的研发投入,差不多是7nm和10nm投入总和。这就导致晶圆厂们在竞相突破新节点的路上,有些玩家会选择中途放弃。比如,联华电子(UMC.N)在2018年8月宣布放弃12nm以下的先进工艺研发;时隔不久,格罗方德宣布放弃7nm的研发。

然而,下游应用非但没有放缓对芯片性能的追求,还对芯片的“占地面积”提出了更高要求。比如TWS耳机、AR和VR等设备体积很小,因此只能将若干个芯片的性能都集中到一块SoC(System on Chip,片上系统)芯片上。

注:右图Mochi为Chiplet最初提出时的名字

注:右图Mochi为Chiplet最初提出时的名字Chiplet就是利用了“高度”这个维度,先将原本在一个平面上的芯片拆分开来,再像积木一样拼装成块。这样不但能够节省占地面积,使得每个小芯片有更大的空间,还能够带来更高的经济效益。

首先,Chiplet可以单独流片(试生产),降低流片失败的风险。随着技术节点的不断提升,单颗芯片集成的IP(大芯片的功能模块)会越来越多。根据IBS数据,7nm、5nm工艺集成的IP数量分别为178、218个。在流片时,任意一个IP出错都会导致流片失败,对芯片设计公司现金流造成一定的冲击。比如7nm工艺芯片一次流片需要3000万元成本,5nm则在4700万以上。

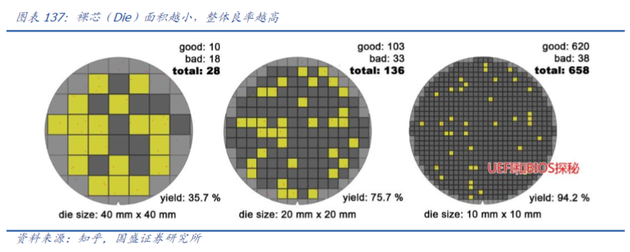

其次,Chiplet能够提升制造的良率。“芯片是沙子做的,但芯片却容不得‘一粒沙子’”,一位业内人士向36氪表示。事实上,芯片是在高度无尘的环境下生产的,其对环境的洁净度要求比手术室还要高。这是因为只要一粒灰尘落到芯片上就可能会导致芯片失效。

灰尘的落下往往又具有随机性,完全不可预测。换句话说,芯片越大,沾染灰尘的可能性就越大,整体的良率就越低。国盛证券数据显示,当芯片整体面积在10mm X 10mm时,良率达94.2%;但如果面积增加至原来的16倍,也就是40mm X 40mm时,良率仅35.7%。

注:图中die表示裸片,即芯片封装前的状态

注:图中die表示裸片,即芯片封装前的状态最后,Chiplet能够提升可靠性。由于芯片制造端的限制,一枚芯片只能采用同一个技术节点。对集成了多个功能的SoC芯片来说,更高的技术节点反而会降低可靠性。比如模拟电路相关的IP就适合使用更成熟的工艺,更低的技术节点。追求过小的线宽可能会出现漏电、噪音等问题。

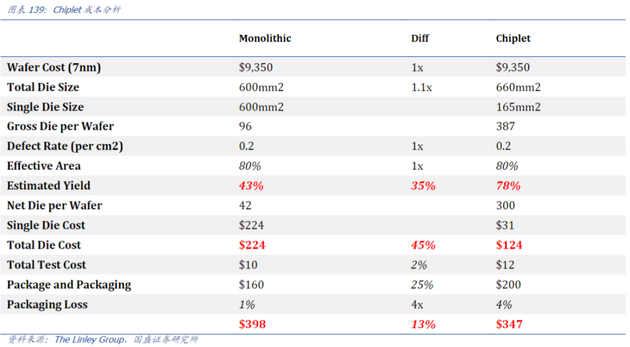

上述优势让Chiplet相较于继续突破先进制程更具性价比。咨询公司The Linley Group测算,在7nm工艺下,Chiplet相较于传统的单芯片方案节省成本近13%。

另外需要说明的是,Chiplet并不是在每一项花费上都优于传统的解决方案,在测试和封装环节,将一个大的芯片分成若干的小芯片反而增加了工作难度和工作量。根据Group测算,在7nm制程这两个环节就分别需要多2%、25%的成本。

剩下的,交给封装

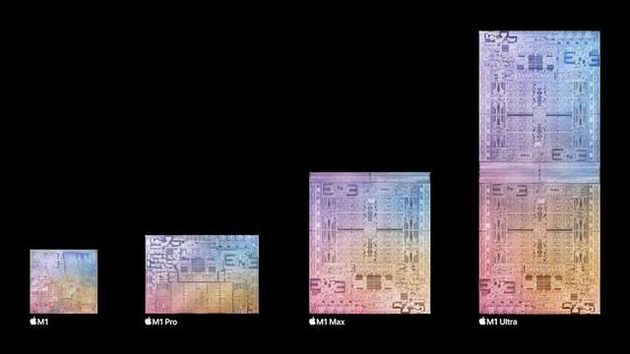

虽然Chiplet技术还未成熟,但一些金字塔尖的玩家已经开始了早期探索。比如苹果发布的M1 Ultra芯片,就是在M1 Max的基础上,采用苹果的桥接技术,将两颗5nm工艺的M1 Max芯片连在一起。

(苹果M1 Max & M1 Ultra,图源网络)

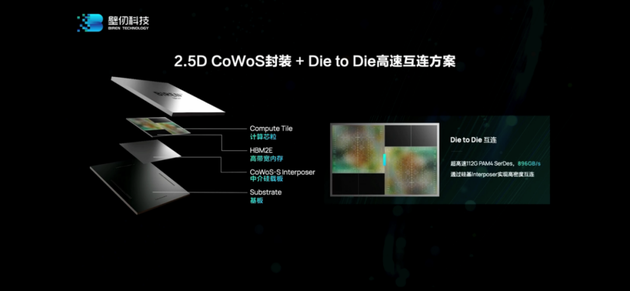

(苹果M1 Max & M1 Ultra,图源网络)近日,壁仞发布的GPU芯片BR100、BR104也是采用了上述方案。壁仞科技联合创始人兼CTO洪洲在发布会上表示,“壁仞科技此次发布的BR104为单die(裸片)产品,而BR100则是采用了Chiplet技术的双die产品。一次流片,形成两款产品,各有优势与侧重点,覆盖更广泛的应用市场。”

(BR100采用Chiplet技术,图源网络)

(BR100采用Chiplet技术,图源网络)值得注意的是,壁仞科技产品与苹果产品是采用了不同的封装技术将两枚芯片“拼接”在一起。除此之外,AMD、Intel等国际知名芯片公司也都开始布局Chiplet,但还只是局限于自家的产品,不同芯片公司出厂的芯片无法兼容。

类似手机充电口和充电线之间的关系,即使现在有了type-C,充电设备之间兼容性还有提升的空间。何况在type-C面世之前,充电口更是五花八门。组成一个芯片系统的小芯片在现在也有很多的接口标准,比如有AMD、ARM等公司所在的Gen Z联盟;Intel、思科等公司所在的CXL联盟等等。

而现在,类似type-C地位的芯片标准统一已经在进行中。2022年Q1,半导体行业头部公司组成了Chiplet标准联盟——UCle(Universal Chiplet Interconnect Express,通用芯粒互联)就定义了Chiplet的连接标准,目的是组建芯片互连生态。有了这个生态,一些成熟的IP在单独流片之后,可以由芯片设计公司外采,降低芯片设计的成本,缩减研发时间。

事实上,除接口标准外,Chiplet还有三大需要解决的问题。

其一,Chiplet在同样的晶体管密度下,发热量更高。这是因为芯片和芯片之间的互联互通始终不如晶体管相连来得直接。虽然在同等面积下塞了更多的晶体管,但功耗成了下一个需要平衡的问题;其二,目前还未推出相关的EDA软件;

其三,Chiplet并不是简单的拼乐高。芯片和芯片的相连,需要将两颗裸片钻孔,再通过精密的电镀手法将电路引出相连。比如钻孔环节,晶圆厚度仅100微米左右(1米=10^6微米),在这样的厚度下钻孔需要微米级的精度控制,控制得不好晶圆就会被钻穿。

即使面临诸多的挑战,Chiplet仍然是后摩尔时代芯片发展的趋势所向。