选自spectrum.ieee.org

作者:Samuel K. Moore

机器之心编译

编辑:陈萍

2D 材料可以使晶体管尺寸进一步缩小,是拓展摩尔定律可行的一个方案。

早在 1965 年,计算机科学家戈登 · 摩尔(Gordon Moore)首先提出假设:集成电路上可以容纳的晶体管数目在大约每经过 18 个月便会增加一倍,同时计算机的运行速度和存储容量也翻一番。这就是半导体领域著名的摩尔定律。现在,一个指甲大小的芯片可以承载数百亿个晶体管,与此同时,可以塞进单个芯片的晶体管数量几乎达到了极限。

为了让摩尔定律继续下去,你可能会想到把晶体管缩小到只有原子厚度。不幸的是,这种想法不适用于硅。因为硅的半导体特性需要第三维度。但有一类材料可以充当半导体,尽管它们是二维的。一些芯片公司和研究机构最新结果表明,一旦硅达到极限,这些 2D 半导体可能是一个很好选择。

近日,在旧金山举行的 2021 IEEE 国际电子设备会议 (IEDM 2021) 上,来自英特尔、斯坦福和台积电的研究人员针对制造 2D 晶体管最棘手的障碍之一提出了单独的解决方案:在半导体与金属接触的地方有尖锐的电阻尖峰。与此同时,来自校际微电子中心 IMEC 的工程师展示了他们如何为商业级晶体管制造工艺扫清道路,并展示了未来 2D 晶体管最小会达到什么程度。此外,来自北京和武汉的研究人员已经构建了硅器件 2D 等效物。

英特尔、斯坦福和台积电等探索 2D 半导体

来自斯坦福大学的电气工程教授 Krishna Saraswat 表示:硅已经达到极限,人们声称摩尔定律已经结束,但在我看来情况并非如此。摩尔定律可以继续进入第三维度。为此,我们需要 2D 半导体或类似的东西。Saraswat 教授与同来自斯坦福大学的 Eric Pop 教授和 H.-S. Philip Wong 教授一起研究 3D 芯片。

2D 半导体属于一类称为过渡金属二硫属化物(transition metal dichalcogenides)的材料。其中,研究最广泛的是二硫化钼(MoS_2)。理论上,与二硫化钼相比,电子应该更快的穿过二硫化钨(另一种 2D 材料)。但在英特尔的实验中,二硫化钼器件更胜一筹。

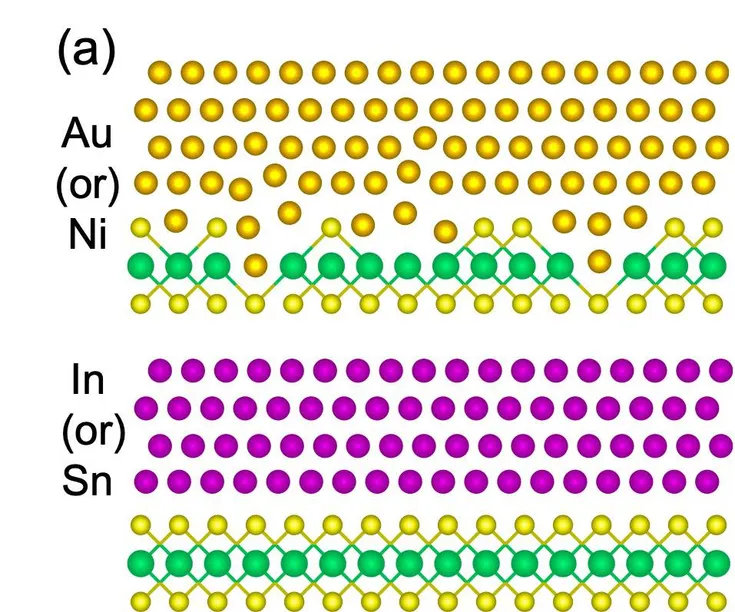

在之前的研究中,金是与二硫化钼形成晶体管的首选触点,但是沉积金(depositing gold)和其他高熔点金属会损坏二硫化钼。因此,Krishna Saraswat 教授学生 Aravindh Kumar 试验了熔点在数百摄氏度以下的铟和锡。

但铟和锡熔点值太低,以至于在芯片后期的加工和封装过程中(这时芯片暴露在高达 300-500 摄氏度的温度下)这些金属会熔化。更糟糕的是,这些金属在加工过程中会被氧化。Kumar 通过将低熔点金属与金进行融合,形成合金来解决。首先 Kumar 将铟或锡沉积在二硫化钼上,以保护半导体,然后用金覆盖以隔离氧气。该过程产生了具有 270 欧姆 - 微米电阻的锡金合金和具有 190 欧姆 - 微米电阻的铟金合金,并且这两种合金在至少 450 摄氏度下保持稳定。

沉积金破坏了 2D 半导体。但是铟和锡沉积在二硫化钼上,保护半导体

与 Kumar 研究不同的是,芯片制造商台积电和英特尔找到了不同的解决方案——锑。台积电专门研究低维芯片的 Han Wang 表示,通过使用半金属作为触点材料来降低半导体和触点之间的能量障碍。半金属(例如锑)是一种介于金属和半导体之间且带隙为零的材料,由此产生的肖特基势垒非常低,因而台积电和英特尔设备的电阻都很低。

此前,台积电曾研究过另一种半金属——铋,但它的熔点太低。Wang 表示,锑具有更好的热稳定性,这意味着它与现有的芯片制造工艺更兼容,产生更持久的器件,并允许芯片制造过程的后半部分具有更大的灵活性。

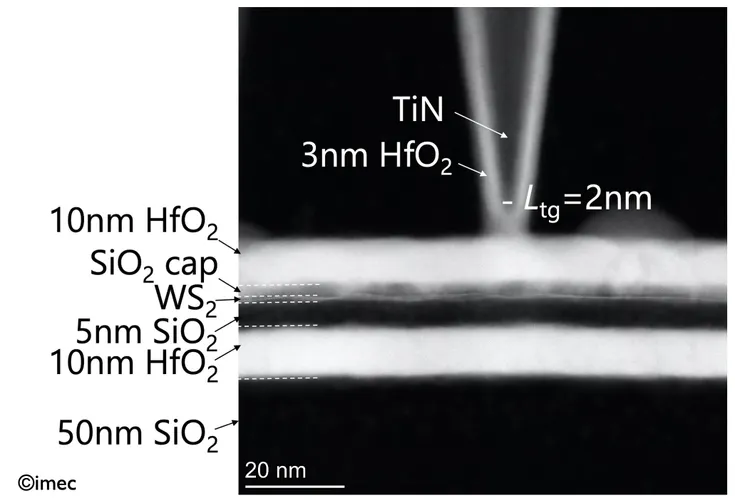

除了制造更好的器件之外,IMEC 的研究人员在探索商用 300 毫米硅晶圆上集成 2D 半导体的途径。使用 300 毫米晶圆,IMEC 探索了 2D 器件最终可以到达多小。研究人员使用二硫化钨作为半导体,进而形成了双栅极晶体管,其中二硫化钨夹在顶部和底部电极之间,控制电流通过。通过使用模式技巧,他们将顶部栅极缩小到 5 纳米以下。但是该特定设备的性能并不理想,不过研究者指出了改进方法。

IMEC 制造了一种栅极长度小于 5 纳米的二硫化钨晶体管

当今,主流的芯片架构采用横向传输场效应晶体管(FET),例如鳍式场效应晶体管(FinFET),因硅体类似鱼背鳍而得名。FinFET 在设计上沿着晶圆表面对晶体管分层,电流沿水平方向流动。但是,为了继续缩小器件的尺寸,同时仍然驱动足够的电流通过,领先的芯片制造商正在转向纳米级器件。

尽管像 IMEC 这样的双栅器件是 2D 研究的标准,但是,来自北京大学和国家脉冲强磁场科学中心的工程师们却更进一步。由吴燕庆教授领导的研究小组使用两层二硫化钼模拟了这种结构。事实证明,该器件不仅仅是其各部分的总和,与其单层器件相比,2D 纳米片的跨导要领先两倍,这意味着对于给定的电压,它可驱动的电流是其他器件的两倍多。

英特尔模拟了更极端版本的堆叠式 2D 器件,研究人员使用了六层二硫化钼和 5 纳米栅极长度,而吴燕庆教授领导研究小组只使用了两层二硫化钼和 100 纳米栅极长度。与具有相同垂直高度和 15 纳米栅极长度的模拟硅器件相比,2D 器件封装在两个纳米薄片中,性能更好。尽管电子通过二硫化钼的速度比通过硅的速度要慢,并且接触电阻要高得多。

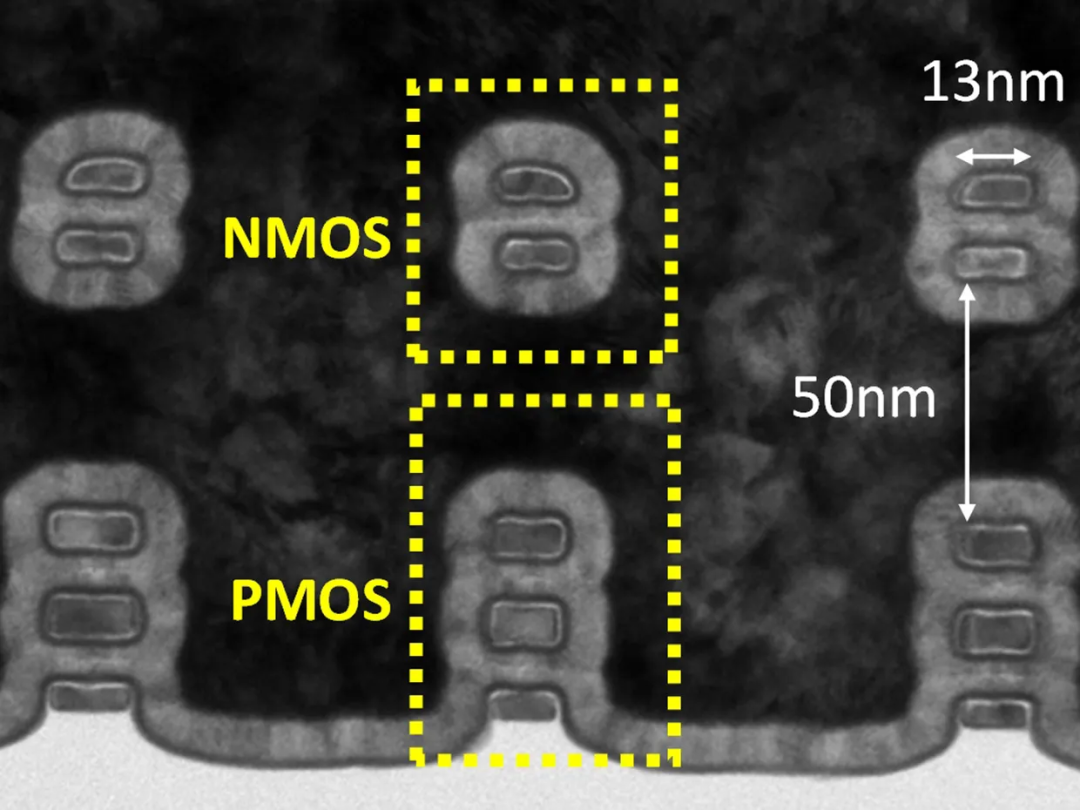

CMOS 芯片由成对的 N-MOS 和 P-MOS 器件组成。为了将更多器件塞入硅片中,芯片制造商希望将这两种类型的器件堆叠在一起,而不是并排排列。在去年 IEDM 上,英特尔展示了这样一种硅器件,称为互补 FET (CFET) 。

NMOS 和 PMOS 器件通常并排放置在芯片上。英特尔找到了一种将它们叠加在一起的方法,从而压缩了电路尺寸。图源:英特尔

NMOS 和 PMOS 器件通常并排放置在芯片上。英特尔找到了一种将它们叠加在一起的方法,从而压缩了电路尺寸。图源:英特尔吴燕庆教授领导的研究小组也尝试了同样的方法,他们用二硒化钨替换堆叠器件中的二硫化钼层。然后,通过修改源极和漏极之间的连接,2D CFET 变成了一个反相器电路,与单个晶体管的占位面积基本相同。

在 2D 半导体获得大规模制造之前,显然还有很多工作要做,但随着接触电阻的进展和新实验的成功,我们可以期待这一领域的发展。

原文链接:https://spectrum.ieee.org/2d-semiconductors-and-moores-law