原标题:AMD大小核专利曝光:或用于下一代锐龙CPU与APU 来源:cnBeta.COM

WCCFTech 刚刚曝光了 AMD 新获的一项有趣专利,因为它预示了下一代锐龙 CPU / APU 产品线可能采用类似移动设备平台的“大小核”设计理念。此前多年,智能机 SoC 厂商已经对 big.LITTLE 架构展开了充分的验证,而英特尔也计划在 12 代 Alder Lake-S 桌面产品线上试水 16C / 24T 的大小核设计。

此前有传闻称,AMD 会在下一代芯片设计中过渡至混合架构,而新曝光的“任务转换”(Task Transition)专利,也或多或少地证实了这一点。

熟悉 ARM SoC 架构的朋友,应该不难理解 big.LITTLE 可结合不同的核心 IP、以实现性能和能效方面的更优均衡。

而英特尔的 12 代 x86 处理器(Lakefield SoC),也设法将高性能的酷睿 Cove 核心、与低功耗的凌动 Gracemont 核心结合到了一起。

虽未得到广泛的采用,但随着英特尔与 AMD 在下一代芯片设计上引领转型,系统和软件开发商也将很快跟进早期测试。

言归正传,AMD 于 2019 年 12 月提交了这项有趣的异构设计专利,且该公司早就在 APU 产品线上实现了“在同一封装中融汇两套不同的芯片 IP”的目标。

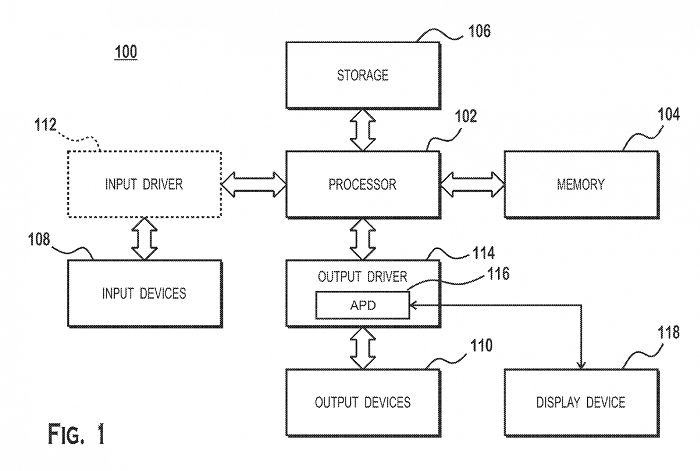

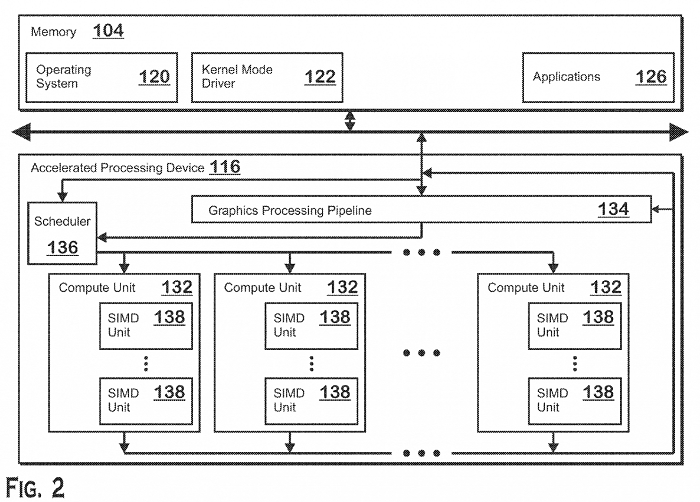

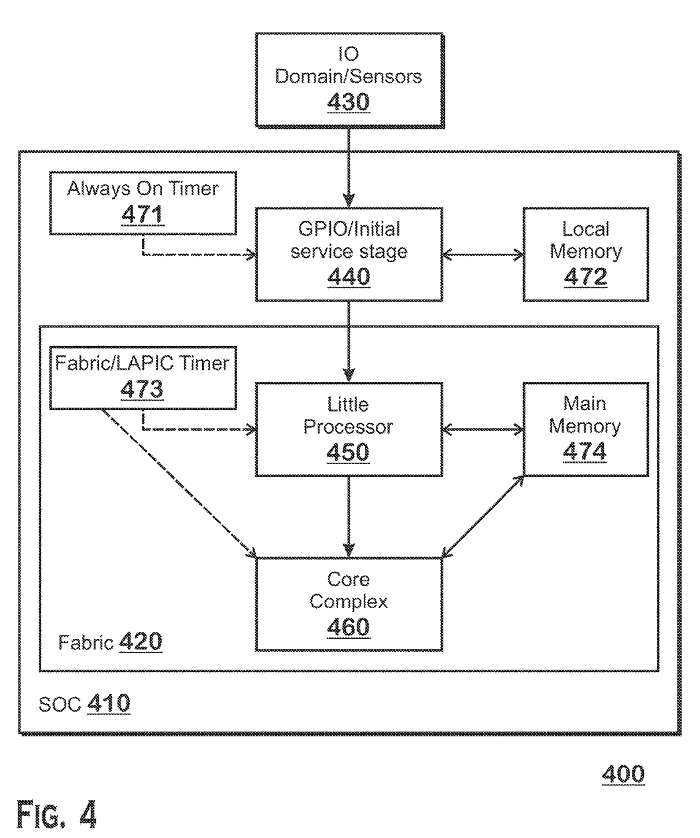

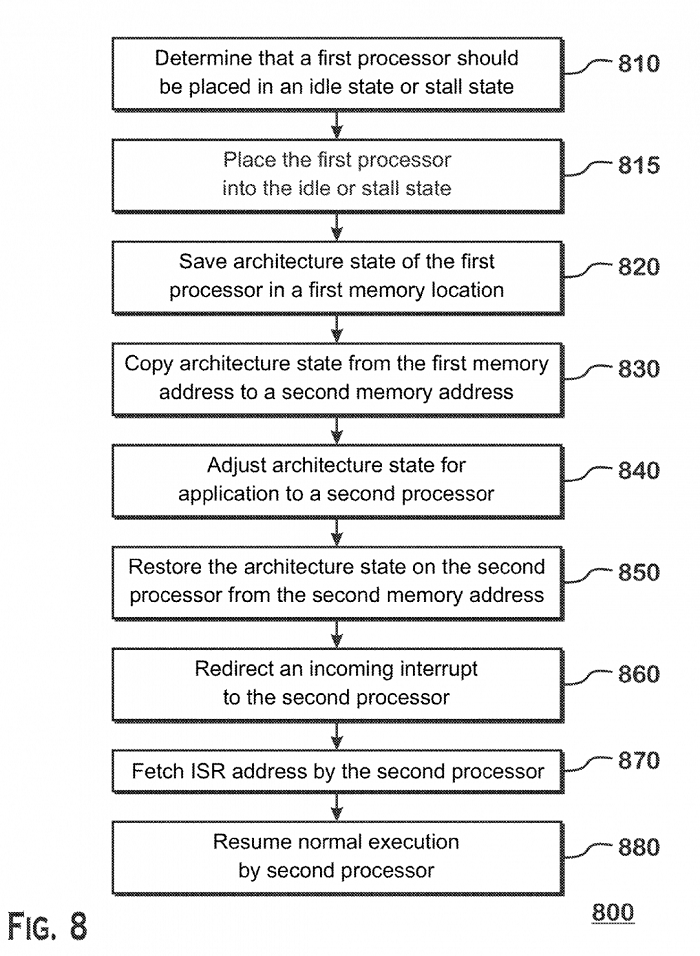

由新专利的文档资料可知,AMD 描述了一种独特的方法、系统和装置,能够将性能度量与相关联的阈值进行比较、或通过其它指标来确定多个任务是否该从某组 CPU 核心转移到另一组。

在工作负载的迁移过程中,显然还需要对两组 CPU 的相关任务进行特定的调整。比如在暂停源 CPU 核心任务的同时、还需要参考目标 CPU 核心的状态信息,以便其做好承接转移负载的准备。

众所周知,异构架构倾向于将大核心用于高性能工作负载、而小核心则更适合于效率优化的多线程任务。

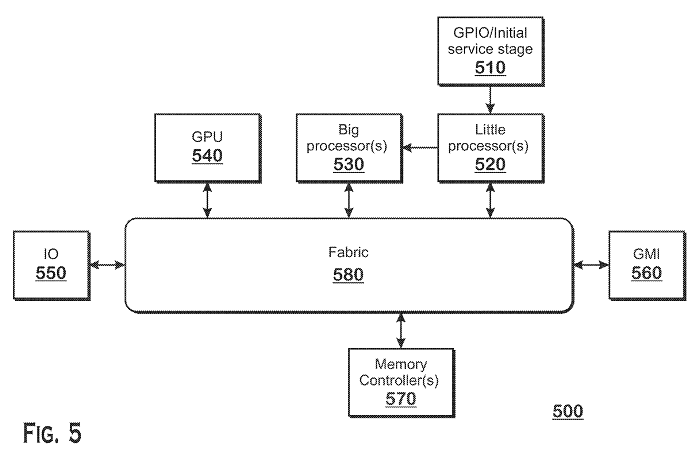

新专利表明,AMD 将通过同一个互连小芯片来沟通两组 CPU 核心、同时给予内部互相通信的权限,以分享核心利用率、内存使用 / 访问、空闲 / 负载状态下的能耗等信息。

最后,有传闻称 AMD 会在 Strix Point APU 芯片上使用 Zen 5 大核心 + Zen 4D 小核心的设计,但它们要等到 2024 年才会与大家见面。

同时随着英特尔 Alder Lake 芯片在今年晚些时候的亮相,预计最新版本的 Windows 操作系统也将为其落实大量更新,以支持混合架构和新的调度优化程序。

至于异构架构能否在 x86 主流平台上交出让广大消费者感到满意的答卷,仍有待时间去检验。