原标题:新思科技推出业界首个面向PCIe 6.0的完整IP解决方案

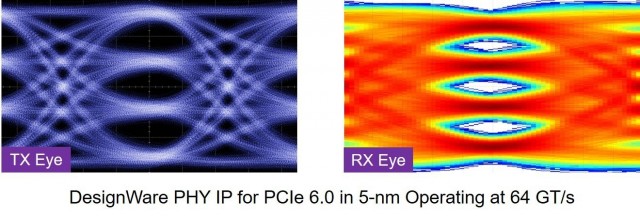

【TechWeb】3月26日消息,新思科技(Synopsys)近日宣布推出业界首个面向PCI Express(PCIe)6.0技术的完整IP核解决方案,其中包括控制器、PHY和验证IP,可实现PCIe 6.0片上系统(SoC)设计的早期开发。基于新思科技广泛部署并经过硅验证的面向PCIe 5.0的DesignWare IP核,面向PCIe 6.0的全新DesignWare IP核支持标准规范的最新功能,其中包括64GT/s PAM-4信号传输、FLIT模式和L0p功耗状态。新思科技的完整IP解决方案可满足高性能计算、AI和存储SoC在延迟、带宽和功耗效率方面不断提高的要求。

为了实现最低延迟并最大限度地提高所有传输规模的吞吐量,面向PCI Express 6.0的DesignWare控制器采用MultiStream架构,可提供相当于Single-Stream设计2倍的性能。该控制器采用1024位架构,可让开发者在1GHz时序收敛的条件下实现64GT/s x 16的带宽。此外,该控制器还可在处理多个数据源以及使用多个虚拟通道时提供最佳流量。为了通过内置验证计划、序列和功能覆盖来加快测试平台的开发,面向PCIe的VC验证IP采用了本地SystemsVerilog/UVM架构,只需小量的工作即可完成集成、配置和定制。

新思科技面向PCIe 6.0的DesignWare PHY IP可提供独特的自适应DSP算法,可优化模拟和数字均衡,从而最大限度地提高功耗效率,而不受通道影响。借助正在申请专利的诊断功能,PHY可实现接近零的链路关闭时间。面向PCIe 6.0的DesignWare PHY IP感知布局架构可最大限度地减少封装串扰,并支持针对x16链路的密集SoC集成。为基于ADC的架构采用优化数据路径可实现超低延迟。

新思科技IP营销和战略高级副总裁John Koeter表示:“云计算、存储和机器学习等领先应用需要传输大量数据,这要求开发者以最小的延迟集成最新的高速接口,以满足这些系统的带宽需求。通过新思科技面向PCI Express 6.0的完整DesignWare IP解决方案,我们的客户可以及早开始其基于PCIe 6.0的设计,并利用新思科技在PCI Express方面的丰富专业知识和卓越领先地位,加速其在芯片领域的成功之路。”

Intel技术计划总监Jim Pappas表示:“PCI Express是历史上使用最广泛、可扩展最强的互连技术。新思科技的最新DesignWare IP是全球生态系统持续致力于PCIe 6.0这一重要行业标准的领先指标,并为PCIe第6代的开发和未来英特尔平台上的应用奠定了基础。”

上市时间和资源

面向PCIe 6.0早期访问的DesignWare控制器和PHY IP计划将于2021年第三季度推出。面向PCIe 6.0的验证IP现已推出。